Cache algorithms

A cache algorithm is an algorithm for controlling a cache memory with the optimized access between a CPU and memory, and inconsistency issues are to be prevented.

Originally, the cache as an intermediate buffer between the CPU and main memory. As the clock frequencies deviated more and more from each other, it was necessary to introduce a buffer ( cache). But we realized early on that you can save a considerable part of the bandwidth of the memory bus to the cache.

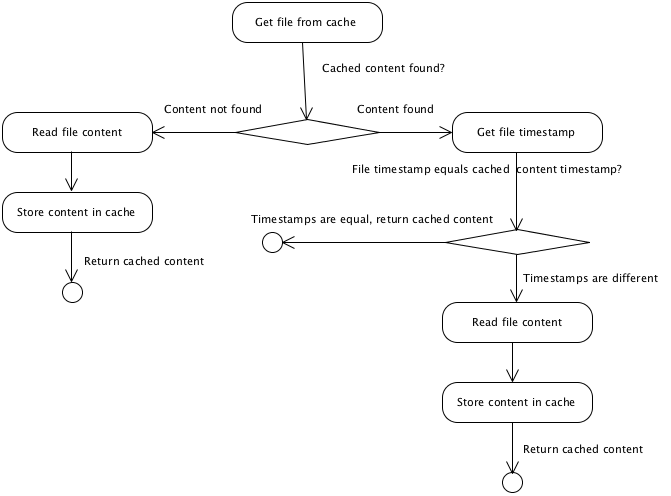

The data are not written directly to memory but in the cache. The method is called write-back (copy -back, store- in ). A block is overwritten in the cache, but also a write to main memory takes place. If a block misses in the cache ( write -miss ), it is first copied into the cache. Then, either written only to the cache ( write- allocate ) or directly in the parent main memory ( no- write- allocate ).

This method is usually used in computer architectures with a single processor. However, it can lead to inconsistencies in I / O operations here.

Multiprocessor systems

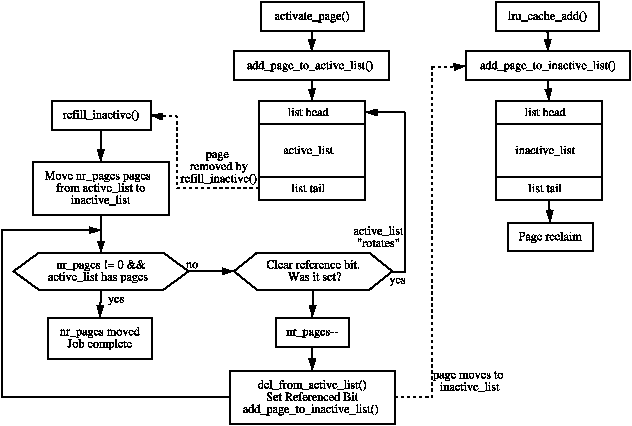

In multiprocessor systems usually each processor has its own cache, and engages over it at a central shared memory. In order to prevent problems due to inconsistencies between the cache and the main memory, a cache algorithm provides for cache coherency.

Write Through ( Write Thru )

It is written by the cache to the main memory. The cache line loses its validity. Therefore, the next read from the cache line is followed by a cache- miss.

Writeback

The data is written back to the cache and the DirtyBit ( = data in main memory and cache are inconsistent ) is set. The comparison with the main memory can be triggered by a FLUSH. In addition, the data is written back to main memory if the cache line is to be used for other data.

Although this technique is more complicated, but also faster than write -through.

Write Allocate

Occurs when writing a cache -miss, so is write- allocate to train. The data will be written directly to the main memory. Then the cache controller causes the newly written data are loaded into the cache.

- Algorithm

- Computer Architecture